線上影音

Home > ANSYS SIwave教學> Guard Trace Effect on 2-Layer PCB

在[如何以兩層板跑DDRII-800]一文中,說明了兩層板與四層板走線的特性阻抗差異,並點出兩層板高速走線伴隨地線(guard trace)的重要性。本文將以SIwave v5.0、Designer v6.0進一步分析兩層板走線伴隨不同密度的地線,對特性阻抗與傳輸線特性的影響,以及地線打ground via的密度、地線是否頭尾接地、地線是否連續沒有中斷...等因素,對傳輸線的影響。

-

伴隨低密度via的地線 (17mm)

1.1 兩條線穿插一條地線

1.2 四條線穿插一條地線

-

伴隨高密度via的地線 (6mm)

2.1 四條線穿插一條地線

-

5.1 DDRIII IBIS下載

5.2 兩條線穿插一條地線

5.3 四條線穿插一條地線

-

6.1 Reference Impedance of Port的影響?

6.2 用SIwave v5.0看TDR時,一次不能看太多訊號?

6.3 兩條線穿插一條地線,改成四條線穿插一條地線,有何好處?

![]()

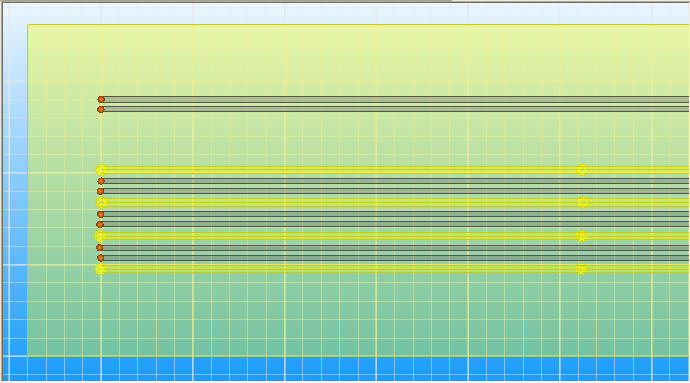

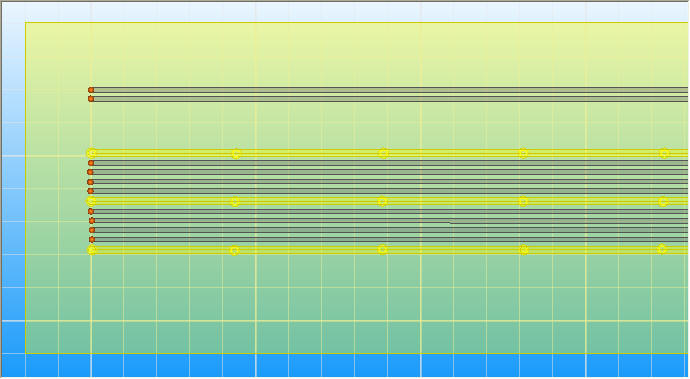

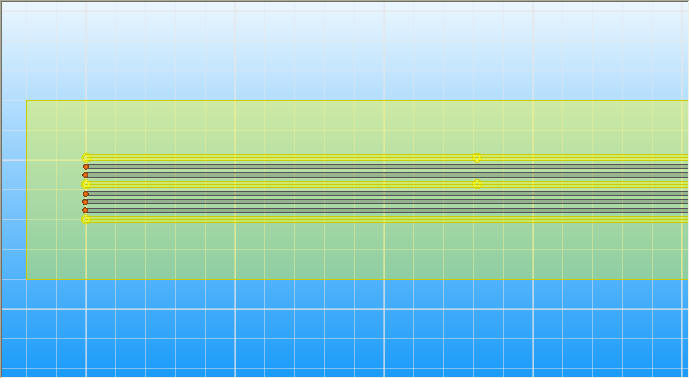

下圖走線線寬7mils、線距7mils(走線邊緣到邊緣)、貫孔直徑5mils、ground guard trace線寬10mils、線長50mm,板厚1.6mm;分別是走線不伴隨地線、兩條走線伴隨一條地線、四條走線伴隨一條地線。

-

伴隨低密度via的地線 (17mm)

1.1 兩條線穿插一條地線

T03~T08是一樣的結構,S21應該都差不多,從此例的模擬結果看來,SIwave v5.0的準度大概到25GHz。而Ansoft的官方說法是SIwave適用於DC~50GHz

為何T01、T02的TDR波形在0.6ns~1.1ns是在65 ohm,而不是50 ohm? 請看問題與討論6.2

1.2 四條線穿插一條地線

從只要有伴隨走地線,不管是兩條線穿插一條地線,或四條線穿插一條地線,S21在20GHz以內的表現都差不多(1dB)。但如果沒有伴隨走地線,在1GHz就可以看出有差異 ,S參數特性差很多。

沒地線伴隨走的訊號,特性阻抗明顯大很多(T01,T02=111 ohm),而只要有伴隨地線,不管是兩條線穿插一條地線,或四條線穿插一條地線,特性阻抗會壓在84~90 ohm之間。這裡的地線並沒有用很寬,筆者地線只用了10mils的線寬,17mm的via間距。

-

伴隨高密度via的地線 (6mm)

2.1 四條線穿插一條地線

打via的密度從17mm縮小到6mm,與step3.1相比,S21在30GHz以內都沒有顯著差別

最下面的地線,除了最左邊有一個ground via,其他的ground via都拿掉

最靠近只有單端接地guard trace的T05,其特性阻抗值相當於沒有伴隨接地,且S21在低頻~20GHz也明顯 較差

5.1 DDRIII IBIS下載

5.2 兩條線穿插一條地線

5.3 四條線穿插一條地線

只考慮PCB的影響,線長50mm、線寬=線距=7mils、Tr=100ps,DDRIII 2033開ODT 120後,四條走線穿插一條地線的眼圖是有差一點。如果要真的判定可不可以用,須再考慮package、bonding貢獻的影響較準

6.1 Reference Impedance of Port的影響?

眼尖的讀者可能有注意到,step1.1中,T01、T02的TDR波形在0.6ns~1.1ns是在65 ohm,而不是50 ohm?

在[TDR Analysis]一文中,筆者有解釋:SIwave或Designer跑出來的TDR波形,右邊會掉下到接近50 ohm(不像一般用網路分析儀量的TDR波形,當走到傳輸線末端時,整個波形是往上飆的),其原因是我們在模擬環境中,傳輸線左右兩端的port都設50 ohm的reference impedance,而不是尾端open。又當傳輸線的特性阻抗是110 ohm,訊號走到右端(尾端)遇到50 ohm的port時,會同時有反射與透射的成份,這就是step1.1中看到的結果。如果我們把T01、T02的右側port de-active,會得到以下波形 ,此時T01、T02的TDR波形,就真的像是用網路分析儀打T01、T02左端所量到的TDR波形了

6.2 用SIwave v5.0看TDR時,一次不能看太多訊號?

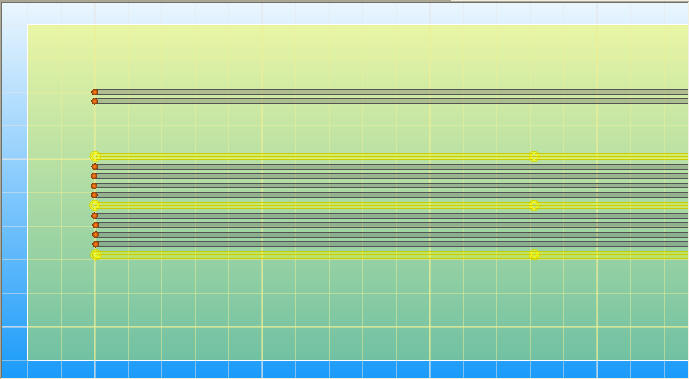

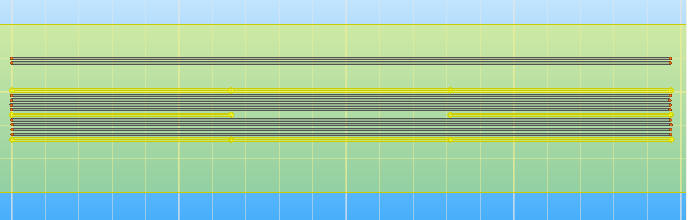

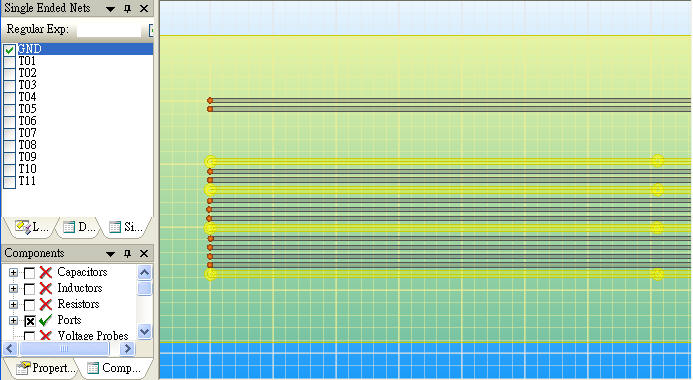

走線由上而下的net name分別是T01~T11

下圖所示為一次看全部11條線的TDR,發現T11的特性阻抗值明顯錯誤(過大)

不知道是不是因為50GHz頻寬太寬了,所以SIwave一次處理太多port會有問題? 但一次看的port數減少就可以避開此問題了

6.3 兩條線穿插一條地線,改成四條線穿插一條地線,有何好處?

當走線速度超過DDRIII 1333時,完全單層PCB走線會造成外圍routing的Addr./Contrl./Cmd. group的走線過長,眼圖會因ISI變得很粗。要繼續把速度撐上去,第一招是在[BGA using 2-layer PCB]所提到的,data group雙面走線(Addr./Contrl./Cmd. group因為沒ODT,不好雙面走線),第二招就是本文所提的,減少guard trace伴隨密度,目標是讓外圍routing的Addr./Contrl./Cmd. group走線長度做到最短,讓PCB佔的SI budget少一些,多一些的budget留給封裝,盡量不用flip chip。

在高速訊號的兩層板PCB設計,四條訊號線穿插一條地線(guard trace),或兩條訊號線穿插一條地線,或guard trace打via的密度,在10GHz頻寬內影響較小,但地線是否頭尾接地、是否整段高速訊號走線有guard trace完整伴隨,影響是很大的,務必遵守。

[1] A. Suntives, A. Khajooeizadeh, "Using Via Fences for Crosstalk Reduction in PCB Circuits", 2006.

[2] Kyoungho Lee, Hyun-Bae Lee, "A Serpentine Guard Trace to Reduce the Far-End Crosstalk Voltage and the Crosstalk Induced Timing Jitter of Parallel Microstrip Lines", 2008.

[3] Eric Bogatin, "Dramatic Noise Reduction using Guard Traces with Optimized Shorting Vias", DesignCon 2013